## **Tutorial** Xilinx Virtex-5 FPGA ML506 Edition

Department of Electrical and Computer Engineering Real-Time DSP and FPGA Development Lab

Mark Sison Manalo and Ashkan Ashrafi

## **Table of Contents**

| Blank Page                                                                                | 3         |

|-------------------------------------------------------------------------------------------|-----------|

| Overview                                                                                  | 4         |

| About this tutorial                                                                       | 4         |

| Software needed                                                                           | 4         |

| Hardware needed                                                                           | 4         |

| Setting up the ML506 board                                                                | 5         |

| The ML506                                                                                 |           |

| Connecting the board                                                                      | 5         |

| Preparing the Compact Flash (Only when necessary)                                         | 10        |

| Running the Xilinx Demo                                                                   | 14        |

| Prerequisites                                                                             |           |

| Programming the FPGA with a VHDL Design Using iMPACT - 2 bit greater than circuit         | 16        |

| Summary                                                                                   | 16        |

| The VHDL Design                                                                           |           |

| Programming the FPGA using iMPACT                                                         |           |

| Hardware Co-Sim with a System Generator created Design Using a Black Box - 2-bit greater- | than from |

| above                                                                                     | 34        |

| Summary                                                                                   | 34        |

| Creating the Design                                                                       |           |

| Using Xilinx XPS and SDK to implement serial communication using the RS232 cable and a    |           |

| program                                                                                   |           |

| Summary                                                                                   |           |

| Xilinx XPS                                                                                |           |

| Xilinx SDK                                                                                |           |

| Play sound with a sine wave using the AC97 codec                                          |           |

| Summary                                                                                   |           |

| Xilinx XPS                                                                                |           |

| Xilinx SDK                                                                                |           |

| Program the FPGA                                                                          |           |

| Programming your FPGA with the Compact Flash                                              |           |

| Summary                                                                                   |           |

| Creating an .ace file                                                                     |           |

| Setting up the Compact Flash                                                              |           |

| Conclusion                                                                                |           |

| More Designs                                                                              | 114       |

Blank Page

## Overview

## About this tutorial

This tutorial will help you familiarize yourself with Xilinx's XtremeDSP Development Platform – Virtex-5 FPGA ML506 Edition. Familiarity of C, VHDL and MATLAB/Simulink would help but it is not required. The ML505/506/507 are the same boards, only the FPGA is different so this tutorial will apply to all of them. Parts of this tutorial are taken from Xilinx tutorials available here:

http://www.xilinx.com/ml506

http://www.xilinx.com/support/documentation/ml506.htm

http://www.xilinx.com/products/boards/ml506/reference\_designs.htm

In addition to the Xilinx documents, the following websites and books were also referenced:

http://www.fpgadeveloper.com/

http://myfpgablog.blogspot.com/2009/12/sysgen-create-new-hwcosim-target-with.html http://academic.csuohio.edu/chu\_p/rtl/fpga\_vhdl.html

### Software needed

- Xilinx ISE Design Suite (version 12.1 and 13.2 is used here)

- Xilinx Platform Studio

- Xilinx Software Development Kit

- Xilinx System Generator

- MATLAB/SIMULINK

- Hyper Terminal / Tera Term / Putty or similar software (search it on Google and install)

- msdosfs.exe with Windows XP (used for reformatting CF in case of file system corruption)

#### Hardware needed

- DVI cable or VGA cable with DVI adapter

- RS232 cable for UART

- Xilinx Platform USB cable

- Speakers or headphones

- Compact Flash reader (to load programs into the compact flash)

## Setting up the ML506 board

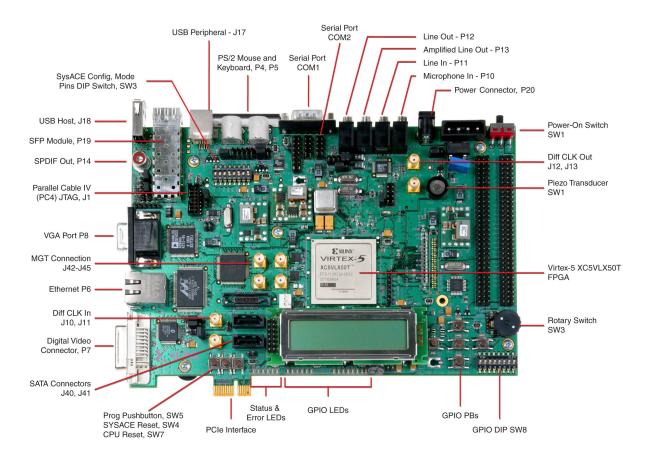

#### The ML506

Here is a picture of the ML506 evaluation board with its components labeled.

### Connecting the board

The board should already be connected in the FPGA lab. If not, please refer to the Xilinx document titled: ml505\_overview\_setup.pdf

For convenience, I will summarize it here.

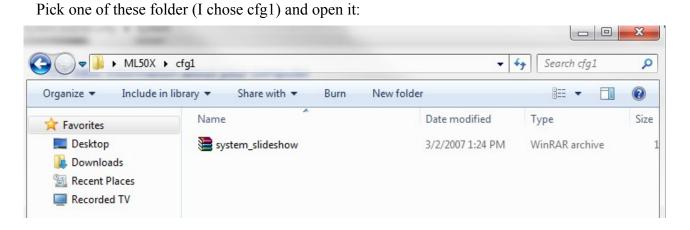

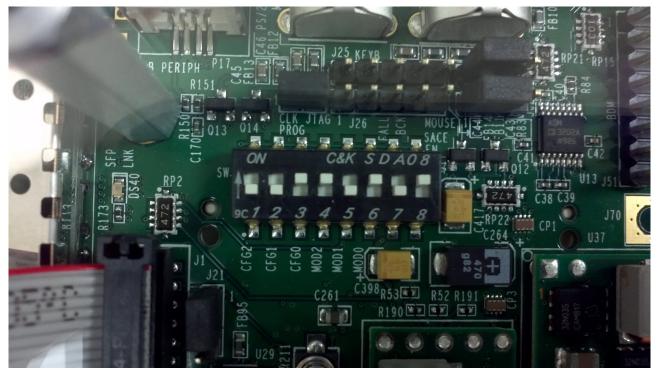

• Set the SW3 switches to 00010101 as shown in the picture:

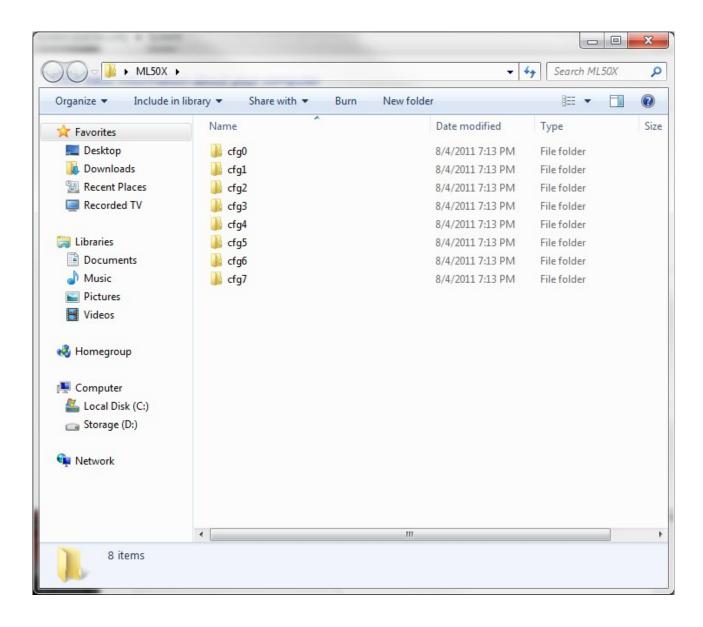

Bits 4-8 (10101) means that on power up, the ML506 board will program the FPGA with the ACE file pointed to by bits 1-3 (in this case: 000). These ACE files are located on the compact flash. 000 means that the ACE file located in cfg0 of the compact flash will be programed into the FPGA. The factory compact flash files has the cfg0 folder containing a system\_bootload .ace file. So if you want to load your own ACE file into folder cfg6 (say). Then you would set SW3 to read 110 10101 if you want cfg7 then SW3 = 111 10101 etc... (Search <u>http://www.fpgadeveloper.com/</u> for a tutorial on creating your own ACE file). But for now lets stick the with factory default files.

| mputer   Removable Disk (F:)   ML50X |                  | ✓ Search ML5. |

|--------------------------------------|------------------|---------------|

| re with 🔻 Burn New folder            |                  |               |

| Name                                 | Date modified    | Type Size     |

| 鷆 cfg0                               | 7/6/2011 9:33 AM | File folder   |

| \mu cfg1                             | 7/6/2011 9:33 AM | File folder   |

| \mu cfg2                             | 7/6/2011 9:33 AM | File folder   |

| \mu cfg3                             | 7/6/2011 9:33 AM | File folder   |

| 퉬 cfg4                               | 7/6/2011 9:33 AM | File folder   |

| \mu cfg5                             | 7/6/2011 9:33 AM | File folder   |

| \mu cfg6                             | 7/6/2011 9:33 AM | File folder   |

| 퉬 cfg7                               | 7/6/2011 9:33 AM | File folder   |

|                                      |                  |               |

- Set SW6 (on the back side of the board) to 11001010

- Connect the Xilinx Platform Cable to PC4 JTAG

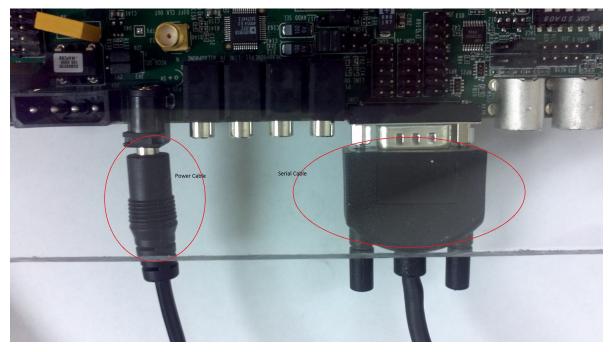

- Connect the Serial cable (RS232) to the PC either directly or with a serial to USB adapter

- Connect the Power cable to the board

• Connect the DVI cable from the ML506 to a monitor.

• Insert the compact flash into the board.

• Install a terminal program such as Tera Term Hyper Terminal or Putty and set it up with the following settings. (On my computer the Serial cable is connected to COM1, yours may differ)

| Tera Term: New c                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | onnection X                                       |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|--|

| © ТСР <u>/І</u> Р                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Hos <u>t</u> : myhost.example.com                 |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ✓ History Service: ○ Telnet TCP port#: 22         |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                   |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | O Other Protocol: UNSPEC ▼                        |  |

| Serial     Se | Po <u>r</u> t: COM1: Communications Port (COM1) - |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | OK Cancel <u>H</u> elp                            |  |

• Go to setup  $\rightarrow$  serial port, and use these settings.

| Tera Term: Serial port setup      | ×                                 |

|-----------------------------------|-----------------------------------|

| Port:                             | СОМ1 - ОК                         |

| <u>B</u> aud rate:                | 9600 -                            |

| <u>D</u> ata:                     | 8 bit - Cancel                    |

| P <u>a</u> rity:                  | none 🔻                            |

| <u>S</u> top:                     | 1 bit • <u>H</u> elp              |

| <u>F</u> low control:             | none -                            |

| Transmit delay<br>0 msec <u>k</u> | <u>c</u> har 0 msec/ <u>l</u> ine |

Now your board should be ready to go. Don't forget to power it on when your ready.

#### Preparing the Compact Flash (Only when necessary)

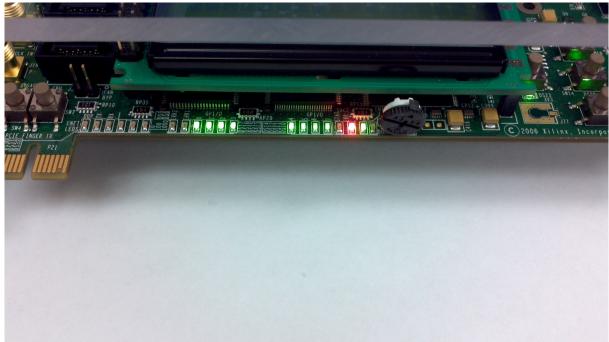

The compact flash should already be formatted correctly as FAT12 or FAT16. After connecting the board insert the compact flash and power up the board. If the CF is not formatted correctly the LED labeled: SACE ERR would be a solid red color as shown in illustration 1.

Illustration 1: SACE ERR, CF card is not being read correctly

In this case, one would need to reformat the CF and place the factory default files back into it. Xilinx provides a tutorial on how to do this:

http://www.xilinx.com/products/boards/ml506/ml506\_12.1/images.htm

However, my attempts at their tutorial using the dd tool did not work. You can try for yourself if you want. (For the records, I tried this using Windows 7 and I am getting either a non-existent file error or a permissions error, even with administrative privileges)

I managed to reformat the CF by another method, described below. (with the help of this: <u>http://www.xilinx.com/support/answers/14456.htm</u>)

If you are going to reformat the CF, follow the directions carefully. Failure to do so might cause the primary hard drive to be erased .

The following items are required:

- Windows XP (I have not confirmed that it works with Windows 7, you can try though)

- mkdosfs.exe (<u>http://www.plunder.com/MKDOSFS-for-Windows-Format-drives-larger-than-32GB-as-FAT-or-FAT32-download-f738e8fe97.htm</u>)

- Compact flash reader (order at Newegg.com, or some other electronics store)

- ML506 factory CF files, go here: <u>http://www.xilinx.com/products/boards/ml506/ml506\_12.1/images.htm</u>

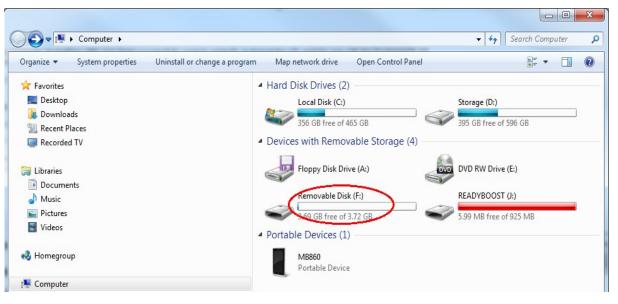

After inserting your CF card into your computer note its drive letter by clicking on Computer.

In my case the drive letter is F: , note that the System ACE controller can only support up to 2GB, the figure above is only for illustrative purposes. The 4GB CF that I have will not work.

Add mkdosfs to your system path: Click start, right-click Computer  $\rightarrow$  Properties  $\rightarrow$ Advanced system settings  $\rightarrow$  Environment Variables. Then edit the 'Path' variable to include the location of where you downloaded mkdosfs.exe. Google how to add to system path for more info.

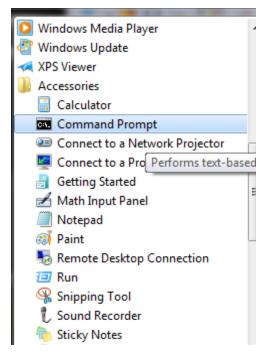

Then open up a command prompt in windows, preferably with administrative privileges (right click command prompt -> run as administrator).

Type the following command:

mkdosfs -v -F 16 F:

Where 'F:' would be changed to your CF drive letter. Leave the first F as '-F'

After this completes, copy and paste the CF factory files into the compact flash as shown:

| Organize ▼ Share with ▼ Burn New fold |              |                    |                     | •== •    | ? |

|---------------------------------------|--------------|--------------------|---------------------|----------|---|

| 🖌 🔆 Favorites                         | Name         | Date modified      | Туре                | Size     |   |

| 🧮 Desktop                             | 3 ML50X      | 7/8/2011 9:38 AM   | File folder         |          |   |

| 鷆 Downloads                           | 🐌 ringtone   | 7/8/2011 9:38 AM   | File folder         |          |   |

| 🕮 Recent Places                       | 📥 demo       | 10/28/2004 12:13   | VLC media file (.bi | 12 KB    |   |

| Recorded TV                           | 🛃 image01    | 1/24/2007 10:10 AM | Bitmap image        | 901 KB   |   |

|                                       | 🛃 image02    | 11/17/2006 9:43 AM | Bitmap image        | 901 KB   |   |

| 4 🥽 Libraries                         | 🛃 image03    | 11/17/2006 12:42   | Bitmap image        | 901 KB   |   |

| Documents                             | 🛃 image04    | 11/17/2006 12:41   | Bitmap image        | 901 KB   |   |

| 🖻 🌙 Music                             | 🛃 image05    | 11/17/2006 12:41   | Bitmap image        | 901 KB   |   |

| Pictures                              | 🛃 image06    | 11/17/2006 12:41   | Bitmap image        | 901 KB   |   |

| Videos                                | 🛃 image07    | 11/17/2006 12:42   | Bitmap image        | 901 KB   |   |

|                                       | 🛃 image08    | 11/17/2006 12:42   | Bitmap image        | 901 KB   |   |

| 🛛 🔣 Homegroup                         | 🛃 image09    | 11/17/2006 9:43 AM | Bitmap image        | 901 KB   |   |

|                                       | README       | 7/7/2006 3:43 PM   | Text Document       | 1 KB     |   |

| 🛿 📜 Computer                          | 📥 sound      | 8/27/2004 2:10 PM  | VLC media file (.w  | 5,513 KB |   |

| 🛛 🚣 Local Disk (C:)                   | 🚳 xilinx.sys | 4/10/2006 8:53 AM  | System file         | 1 KB     |   |

| Storage (D:)                          |              |                    |                     |          |   |

| Removable Disk (F:)                   |              |                    |                     |          |   |

| 🖻 👝 READYBOOST (J:)                   |              |                    |                     |          |   |

| MB860                                 |              |                    |                     |          |   |

Once this is complete, right-click the compact flash and eject it.

| janize 🔻       | Share with 🔻 🛛 Burn 🛛 New folder    |              |                    |                     | •     |

|----------------|-------------------------------------|--------------|--------------------|---------------------|-------|

| Favorites      |                                     | Name         | Date modified      | Туре                | Size  |

| Desktop        |                                     | ML50X        | 7/8/2011 9:38 AM   | File folder         |       |

| Downloads      |                                     | ingtone      | 7/8/2011 9:38 AM   | File folder         |       |

| Recent Plac    | es                                  | 🛓 demo       | 10/28/2004 12:13   | VLC media file (.bi | 12    |

| Recorded T     | v                                   | image01      | 1/24/2007 10:10 AM | Bitmap image        | 901   |

|                |                                     | 🔜 image02    | 11/17/2006 9:43 AM | Bitmap image        | 901   |

| Libraries      |                                     | 🔜 image03    | 11/17/2006 12:42   | Bitmap image        | 901   |

| Documents      | 5                                   | 🛃 image04    | 11/17/2006 12:41   | Bitmap image        | 901   |

| Music 🖉        |                                     | 🛃 image05    | 11/17/2006 12:41   | Bitmap image        | 901   |

| Pictures       |                                     | 🛃 image06    | 11/17/2006 12:41   | Bitmap image        | 901   |

| <b>Videos</b>  |                                     | 🛃 image07    | 11/17/2006 12:42   | Bitmap image        | 901   |

|                |                                     | 🛃 image08    | 11/17/2006 12:42   | Bitmap image        | 901   |

| Homegroup      |                                     | 🛃 image09    | 11/17/2006 9:43 AM | Bitmap image        | 901   |

|                |                                     | README       | 7/7/2006 3:43 PM   | Text Document       | 1     |

| Computer       |                                     | 📥 sound      | 8/27/2004 2:10 PM  | VLC media file (.w  | 5,513 |

| 🍒 Local Disk ( | (C:)                                | 🚳 xilinx.sys | 4/10/2006 8:53 AM  | System file         | 11    |

| Storage (D:)   |                                     |              |                    |                     |       |

| Removable      |                                     |              |                    |                     |       |

| READY          | Expand                              |              |                    |                     |       |

| MB860 🦉        | Add to archive                      |              |                    |                     |       |

|                | Open AutoPlay                       |              |                    |                     |       |

| Network        | Open in new window                  |              |                    |                     |       |

|                | Share with                          |              |                    |                     |       |

|                | Open as Portable Device             |              |                    |                     |       |

|                | Add to "Archive.rar"                |              |                    |                     |       |

|                | Compress and email                  |              |                    |                     |       |

|                | Compress to "Archive.rar" and email |              |                    |                     |       |

|                | Format                              |              |                    |                     |       |

|                | Eject                               |              |                    |                     |       |

|                | Cut                                 |              |                    |                     |       |

|                | Сору                                |              |                    |                     |       |

Insert the CF back into the ML506 and turn on the power. Hopefully, you will have no red SACE ERR.

No SACE ERR

## **Running the Xilinx Demo**

#### Prerequisites

- Make sure you have the board connected to the computer (see—connecting the board)

- Insert the Compact Flash with the factory files loaded into it.

- Connect some headphones or speakers to Line out.

After connecting your board. Run Tera Term/HyperTerminal/Putty with the setting described in the section 'Connecting the Board '.

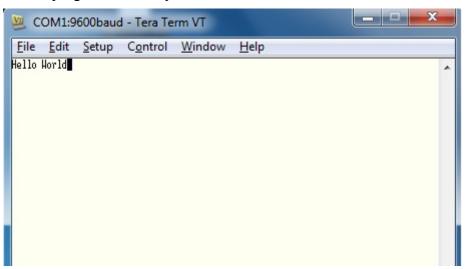

Power up the board and it should start displaying text to the Tera Term window as shown below.

| 🐸 COM1:9600baud - Tera Term VT                                                                                                     |

|------------------------------------------------------------------------------------------------------------------------------------|

| <u>File Edit Setup Control Window H</u> elp                                                                                        |

| Helcome to the Xilinx Virtex-5 ML5D5 Evaluation Platform Bootloader Menu!                                                          |

| Please choose a demo by typing in the number of the demo you want to use                                                           |

| Or select a demo using the directional buttons and LCD or VGA display<br>(Then press the center button to start the selected demo) |

| 1. Virtex-5 Slide Shou<br>2. Heb Server Demo                                                                                       |

| 3. Simon Game                                                                                                                      |

| 4. Board Diagnostics (XROM)<br>5. USB Demo                                                                                         |

| 6. My own ACE file                                                                                                                 |

| 7. Ring Tone Player                                                                                                                |

|                                                                                                                                    |

You can run the demo programs by pressing a number on your PC keyboard that corresponds to your demo of choice.

Also, this demo makes use of the monitor connected to your ML506 via DVI or VGA adapter. Make sure you switch your screen input (press on the buttons in front of you monitor to access the menu) to the ML506 so you can see the video output.

# Programming the FPGA with a VHDL Design Using iMPACT – 2 bit greater than circuit

#### Summary

This tutorial will show you how to program the FPGA with a VHDL design created in ISE. Then we will use 4 switches and 1 led on the ML506 board to simulate the design. We will not go over the VHDL code as it is beyond the scope of this tutorial. After finishing this tutorial, you should be able to program the FPGA with your own circuit design and connect it to some GPIO (general purpose input/output) pins.

## The VHDL Design

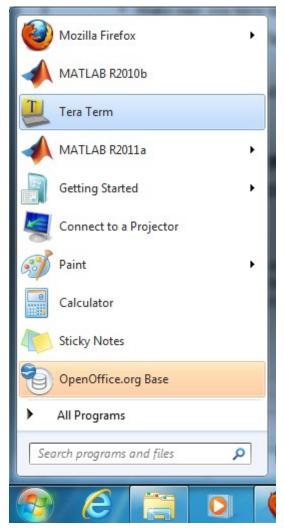

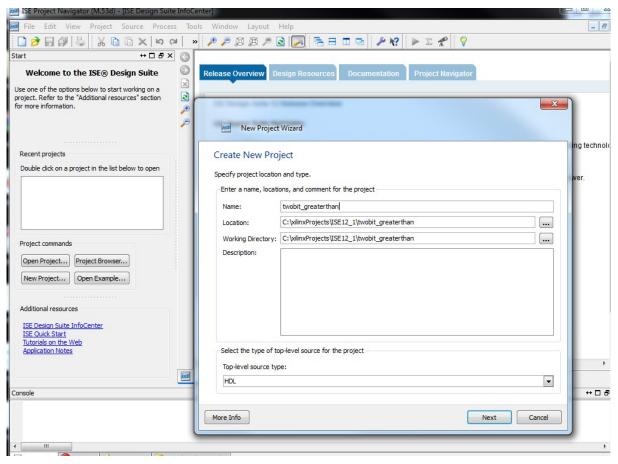

Open up Xilinx ISE.

Click File--> New Project.

Set the location of your project file, to avoid any errors later on, make sure there are no spaces in the file path you choose.

Then name your project something descriptive like : twobit greaterthan.

Make sure the top-level source is HDL.

Click Next.

| Now setu  | n the | project | settings | for the | ML 506   | as shown | below a | and cl | ick Next  | and Finish. |

|-----------|-------|---------|----------|---------|----------|----------|---------|--------|-----------|-------------|

| TNOW SCIU | p inc | project | soungs   | ior unc | IVIL JUU | as shown |         | inu ci | ICK INCAL | and Finish. |

| Project Settings                             |                               |   |

|----------------------------------------------|-------------------------------|---|

| Specify device and project properties.       |                               |   |

| Select the device and design flow for the pr | roject                        |   |

| Property Name                                | Value                         |   |

| Product Category                             | All                           | [ |

| Family                                       | Virtex5                       | [ |

| Device                                       | XC5VSX50T                     | [ |

| Package                                      | FF1136                        | [ |

| Speed                                        | -1                            | [ |

|                                              |                               |   |

| Top-Level Source Type                        | HDL                           |   |

| Synthesis Tool                               | XST (VHDL/Verilog)            | [ |

| Simulator                                    | ISim (VHDL/Verilog)           |   |

| Preferred Language                           | VHDL                          |   |

| Property Specification in Project File       | Store non-default values only | [ |

| Manual Compile Order                         |                               |   |

| VHDL Source Analysis Standard                | VHDL-93                       | [ |

|                                              |                               |   |

| Enable Message Filtering                     |                               |   |

A 2-bit greater-than circuit can be realized as a sum of products, namely,

agreatb = a(1)b(1)' + a(0)b(1)'b(0)' + a(1)a(0)b(0)'

where *a* and *b* are the 2-bit inputs and *agreatb* is the output.

First we will write the VHDL file that implements the circuit, then we will connect inputs a and b to 4 switches and the output agreatb to an led using a universal constraints file.

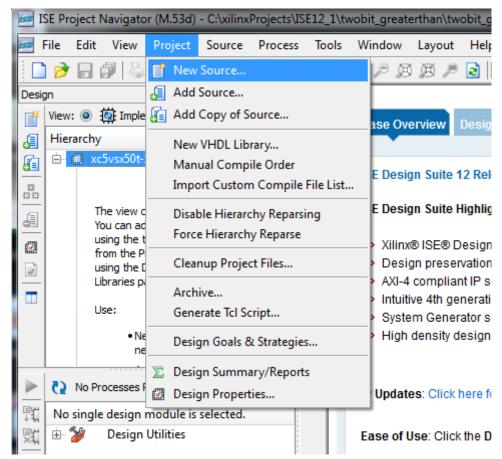

Highlight the xc5vsx50t in the Hierarchy window, then at the top menu click Project  $\rightarrow$  New Source.

Select VHDL module and name the file 'greater\_2bit', click Next.

| <ul> <li>New Source Wizard</li> <li>Select Source Type</li> <li>Select source type, file name and its location.</li> <li>Select source type, file name and its location.</li> <li>IP (CORE Generator &amp; Architecture Wizard)</li> <li>Schematic</li> <li>User Document</li> <li>Verilog Module</li> <li>Verilog Test Fixture</li> <li>VHDL Module</li> <li>VHDL Library</li> <li>VHDL Package</li> <li>VHDL Test Bench</li> <li>Embedded Processor</li> </ul> | Eile name:<br>greater_2bit<br>Logation:<br>C:\xilinxProjects\ISE12_1\twobit_greaterthan |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

| More Info                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Next Cancel                                                                             |

In the define module screen change the architecture name to 'sop\_arch' for sum-of-products architecture. We have two inputs, a and b, each two bits wide and one output 'agreatb'. Click Next and Finish.

| Define Modu         | le           |        |      |          |     |     |

|---------------------|--------------|--------|------|----------|-----|-----|

| Specify ports for I | module.      |        |      |          |     |     |

|                     | greater_2bit |        |      |          |     |     |

| Architecture name   | sop_arch     |        |      |          |     |     |

|                     | Port Name    | Direct | tion | Bus      | MSB | LSB |

| a,b                 |              | in     | -    | <b>V</b> | 1   | 0   |

| agreatb             |              | out    | -    |          |     |     |

|                     |              | in     | -    |          |     |     |

|                     |              | in     | -    |          |     |     |

|                     |              | in     | -    |          |     |     |

|                     |              | in     | -    |          |     |     |

|                     |              | in     | -    |          |     |     |

|                     |              | in     | -    |          |     |     |

|                     |              |        |      | 12 C     |     |     |

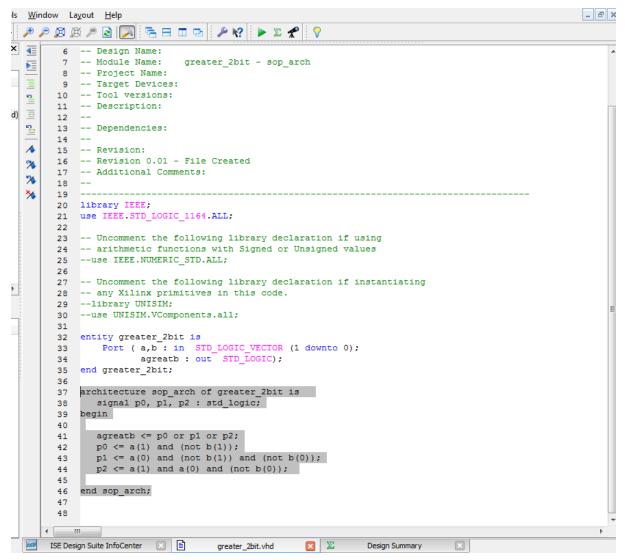

Xilinx should now have created a VHDL template for use to write our code in. If you don't see it double click on the file 'greater\_2bit – sop\_arch' in the hierarchy window.

Change the architecture definition to this:

```

architecture sop_arch of greater_2bit is

signal p0, p1, p2 : std_logic;

```

begin

```

agreatb <= p0 or p1 or p2;

p0 <= a(1) and (not b(1));

```

$p1 \le a(0)$  and (not b(1)) and (not b(0));  $p2 \le a(1)$  and a(0) and (not b(0));

end sop\_arch;

Click save.

Now that we have our circuit realized in code, we will connect the inputs and outputs ,a,b,agreatb, to some switches and an led.

To do this we must know the pin numbers of the FPGA. They can be found here:

http://www.xilinx.com/products/boards/ml505/ml505\_12.1/docs/ml50x\_U1\_fpga.ucf

## We are interested in these pin locations:

|                  | ,,,,,,                                                          |

|------------------|-----------------------------------------------------------------|

| NET FPGA VRN B21 | LOC="AJ25"; # Bank 21, Vcco=1.8V, DCI using 49.9 ohm resistors  |

| NET FPGA VRN B22 | LOC="AF8"; # Bank 22, Vcco=3.3V, DCI using 49.9 ohm resistors   |

| NET FPGA VRP B11 | LOC="M33"; # Bank 11, Vcco=2.5V or 3.3V user selectable by J20  |

| NET FPGA VRP B13 | LOC="AH33"; # Bank 13, Vcco=2.5V or 3.3V user selectable by J20 |

| NET FPGA VRP B17 | LOC="AE31"; # Bank 17, Vcco=1.8V, DCI using 49.9 ohm resistors  |

| NET FPGA VRP B19 | LOC="M27"; # Bank 19, Vcco=1.8V, DCI using 49.9 ohm resistors   |

| NET FPGA VRP B20 | LOC="L11"; # Bank 20, Vcco=3.3V, DCI using 49.9 ohm resistors   |

| NET FPGA VRP B21 | LOC="AH25"; # Bank 21, Vcco=1.8V, DCI using 49.9 ohm resistors  |

| NET FPGA VRP B22 | LOC="AE9"; # Bank 22, Vcco=3.3V, DCI using 49.9 ohm resistors   |

| NET GPIO DIP SW1 | LOC="U25"; # Bank 15, Vcco=1.8V, DCI using 49.9 ohm resistors   |

| NET GPIO DIP SW2 | LOC="AG27"; # Bank 21, Vcco=1.8V, DCI using 49.9 ohm resistors  |

| NET GPIO DIP SW3 | LOC="AF25"; # Bank 21, Vcco=1.8V, DCI using 49.9 ohm resistors  |

| NET GPIO DIP SW4 | LOC="AF26"; # Bank 21, Vcco=1.8V, DCI using 49.9 ohm resistors  |

| NET GPIO DIP SW5 | LOC="AE27"; # Bank 21, Vcco=1.8V, DCI using 49.9 ohm resistors  |

| NET GPIO DIP SW6 | LOC="AE26"; # Bank 21, Vcco=1.8V, DCI using 49.9 ohm resistors  |

| NET GPIO DIP SW7 | LOC="AC25"; # Bank 21, Vcco=1.8V, DCI using 49.9 ohm resistors  |

| NET GPIO DIP SW8 | LOC="AC24"; # Bank 21, Vcco=1.8V, DCI using 49.9 ohm resistors  |

| NET GPIO LED 0   | LOC="H18"; # Bank 3, Vcco=2.5V, No DCI                          |

| NET GPIO LED 1   | LOC="L18"; # Bank 3, Vcco=2.5V, No DCI                          |

| NET GPIO LED 2   | LOC="G15"; # Bank 3, Vcco=2.5V, No DCI                          |

| NET GPIO LED 3   | LOC="AD26"; # Bank 21, Vcco=1.8V, DCI using 49.9 ohm resistors  |

| NET GPIO LED 4   | LOC="G16"; # Bank 3, Vcco=2.5V, No DCI                          |

| NET GPIO LED 5   | LOC="AD25"; # Bank 21, Vcco=1.8V, DCI using 49.9 ohm resistors  |

| NET GPIO LED 6   | LOC="AD24"; # Bank 21, Vcco=1.8V, DCI using 49.9 ohm resistors  |

| NET GPIO LED 7   | LOC="AE24"; # Bank 21, Vcco=1.8V, DCI using 49.9 ohm resistors  |

| NET GPIO LED C   | LOC="E8"; # Bank 20, Vcco=3.3V, DCI using 49.9 ohm resistors    |

| NET GPIO LED E   | LOC="AG23"; # Bank 2, Vcco=3.3V                                 |

| NET GPIO LED N   | LOC="AF13"; # Bank 2, Vcco=3.3V                                 |

|                  |                                                                 |

At the top click on Project  $\rightarrow$  New Source.

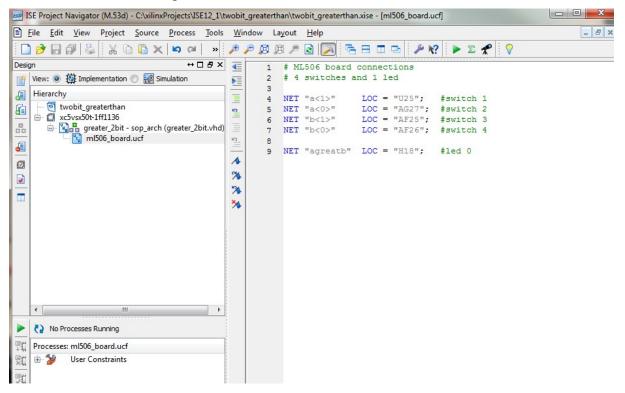

Select Implementation Constraints File and name the file 'ml506\_board'. Click Next and finish.

| Select Source Type<br>Select source type, file name and its location.<br>BMM File<br>ChipScope Definition and Connection File<br>Timplementation Constraints File<br>Inplementation Constraints File<br>IP (CORE Generator & Architecture Wizard)<br>MEM File<br>Schematic<br>User Document<br>Verilog Module<br>Verilog Test Fixture<br>VHDL Module<br>VHDL Library<br>P VHDL Package<br>VHDL Test Bench<br>Embedded Processor | File name:<br>ml506_board<br>Logation:<br>C:\xilinxProjects\ISE12_1\twobit_greaterthan |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

| More Info                                                                                                                                                                                                                                                                                                                                                                                                                       | Add to project                                                                         |

Now you should see a blank file, if not, double-click on 'ml506\_board.ucf' in the hierarchy window.

Enter in the following code and save.

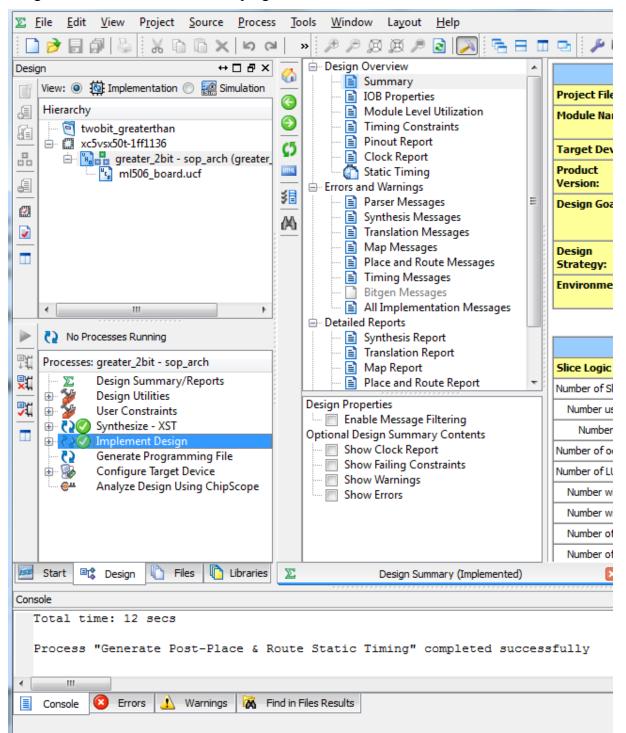

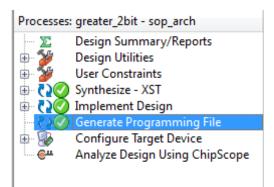

Now that our code is finished we have to implement the design and generate the bitstream. Highlight 'greater\_2bit -sop\_arch' in the Hierarchy window, then in the processes window below it, double-click 'Implement Design' after it finishes double-click 'Generate Programming File', this will generate the bistream needed to program the FPGA.

After Xilinx finishes generating the programming file, you can find it inside your project directory.

| 퉬 xst                    | 7/15/2011 10:15 AM | File folder      |

|--------------------------|--------------------|------------------|

| greater_2bit.bgn         | 7/15/2011 10:19 AM | BGN File         |

| greater_2bit.bit         | 7/15/2011 10:19 AM | BIT File         |

| greater_2bit.bld         | 7/15/2011 10:16 AM | BLD File         |

| greater_2bit.cmd_log     | 7/15/2011 10:19 AM | CMD_LOG File     |

| greater_2bit.drc         | 7/15/2011 10:19 AM | DRC File         |

| greater_2bit_envsettings | 7/15/2011 10:19 AM | Firefox Document |

| greater_2bit_summary     | 7/15/2011 10:19 AM | Firefox Document |

| usage_statistics_webtalk | 7/15/2011 10:19 AM | Firefox Document |

| twobit_greaterthan.gise  | 7/15/2011 10:19 AM | GISE File        |

| greater_2bit.lso         | 7/12/2011 11:18 AM | LSO File         |

| areater 2bit map.map     | 7/15/2011 10:16 AM | MAP File         |

## Programming the FPGA using iMPACT

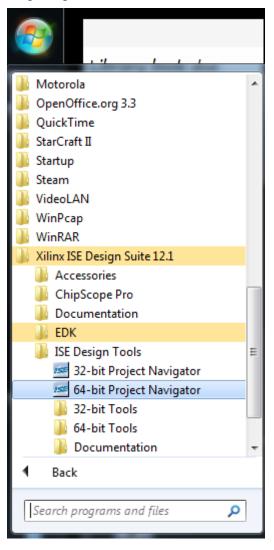

Now its time to program the FPGA. Close Xilinx ISE and open up iMPACT.

| Xilinx ISE Design Suite 12.1    |

|---------------------------------|

| Accessories                     |

| 퉬 ChipScope Pro                 |

| Documentation                   |

| 🔒 EDK                           |

| 퉬 ISE Design Tools              |

| 32-bit Project Navigator        |

| 54-bit Project Navigator        |

| 🍌 32-bit Tools                  |

| 퉬 64-bit Tools                  |

| ar Constraints Editor           |

| 🏹 CORE Generator                |

| 🔯 FPGA Editor                   |

| impact                          |

| 陷 Simulation Library Compilatio |

| 🔞 Timing Analyzer               |

| XPower Analyzer                 |

| 4 Back                          |

|                                 |

| Search programs and files       |

|                                 |

| 🔊 ⋵ 🚞 🖸                         |

Cancel all the initial prompts that come up.

Turn on the ML506. If this is your first time turning it on, Windows might automatically install some drivers (allow it to, a restart maybe required).

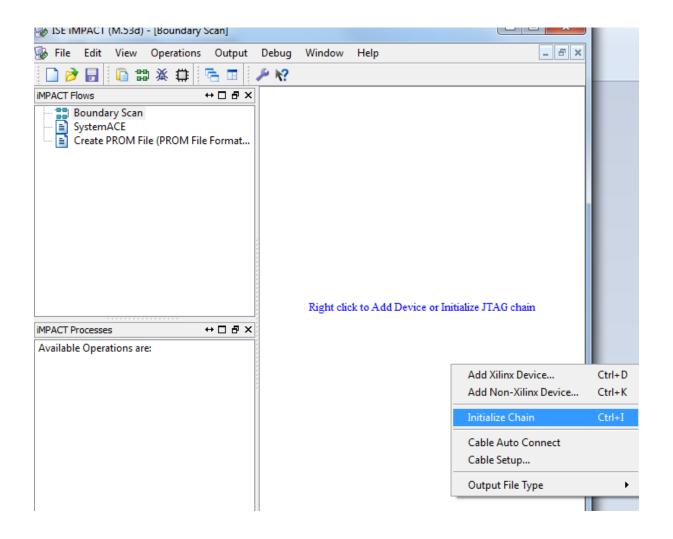

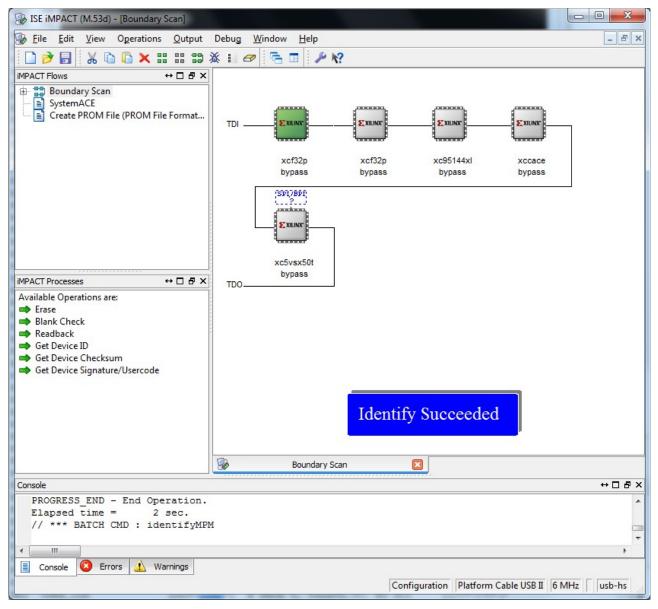

Double-click on 'Boundary Scan', then right-click on the empty plane and click 'Initialize Chain'. If you are getting errors about iMPACT unable to see your board, unplug the USB cable from your ML506 and replug it to initiate some windows auto driver install.

Cancel all the automatic prompts that come up.

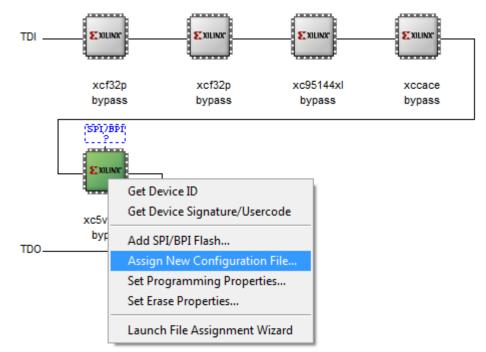

If all is well, you should see the JTAG chain with the Virtex 5 FPGA as well as some PROMs, ACE controller and CPLDs.

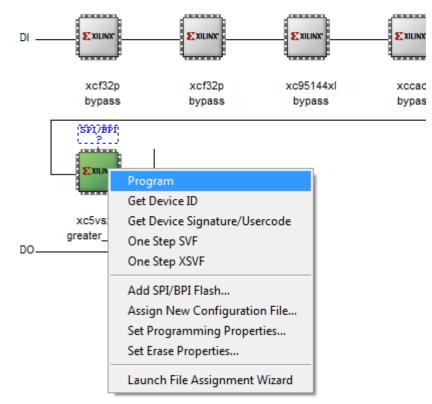

Right-click on the FPGA (xc5vsx50t) and click 'Assign New Configuration File'

then browse to your .bit file.

| Name              | Date modified      | Туре        | Size     |

|-------------------|--------------------|-------------|----------|

| 퉬 _ngo            | 7/15/2011 10:16 AM | File folder |          |

| 퉬 _xmsgs          | 7/15/2011 10:19 AM | File folder |          |

| 퉬 ipcore_dir      | 7/12/2011 10:29 AM | File folder |          |

| 퉬 iseconfig       | 7/15/2011 10:15 AM | File folder |          |

| 퉬 xlnx_auto_0_xdb | 7/15/2011 10:16 AM | File folder |          |

| 퉬 xst             | 7/15/2011 10:15 AM | File folder |          |

| greater_2bit.bit  | 7/15/2011 10:19 AM | BIT File    | 2,444 KB |

That's it! Your 2-bit greater-than circuit should now be operational. Input a is on switch 1 and 2 of the GPIO DIP switch and input b is on switch 3 and 4. Toggle the switches (the tip of a mechanical pencil would help if the switches are too small for your fingers) and if a is greater than b (in binary) then the GPIO led0 will light up, else it will stay dark.

. LEDO lights up when A is greater than B In this case A = '10' = 2 B = '00' = 0, so A is greater than B Inc A = '01' = 1 B = '10' = 2 So A is less than B A is less than B so LEDO stays dark

## Hardware Co-Sim with a System Generator created Design Using a Black Box – 2-bit greater-than from above

#### Summary

This builds off of a tutorial I found here:

http://myfpgablog.blogspot.com/2009/12/sysgen-create-new-hwcosim-target-with.html

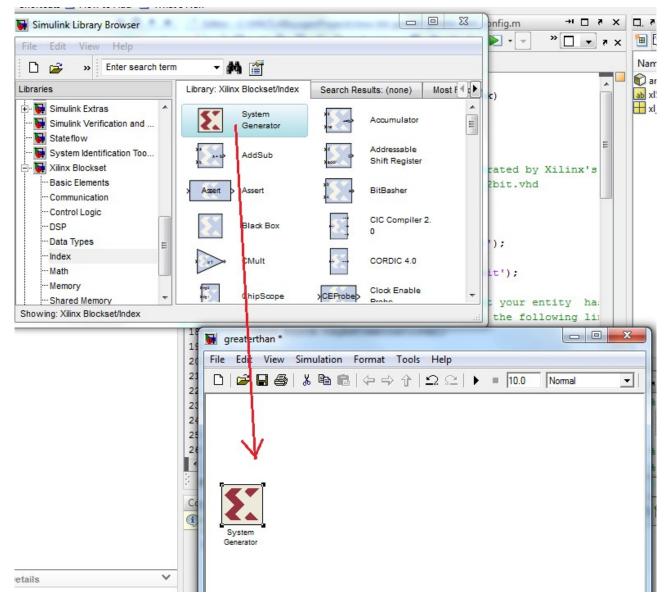

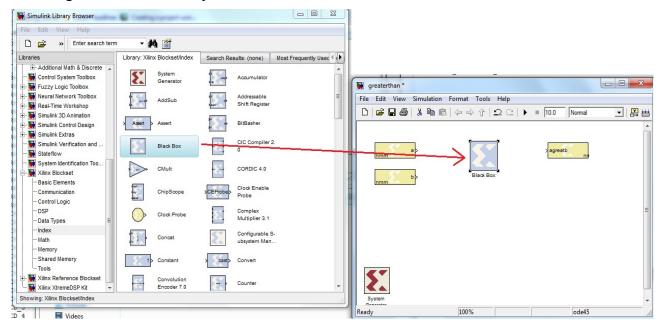

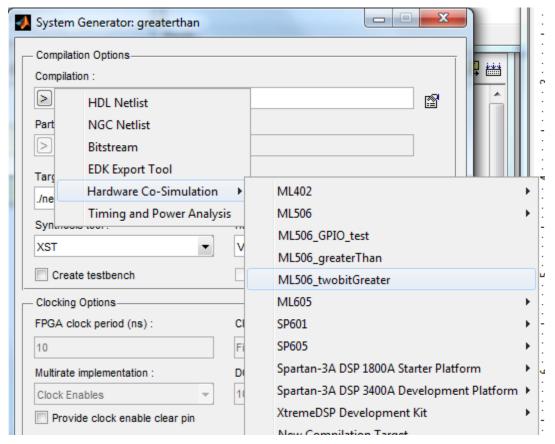

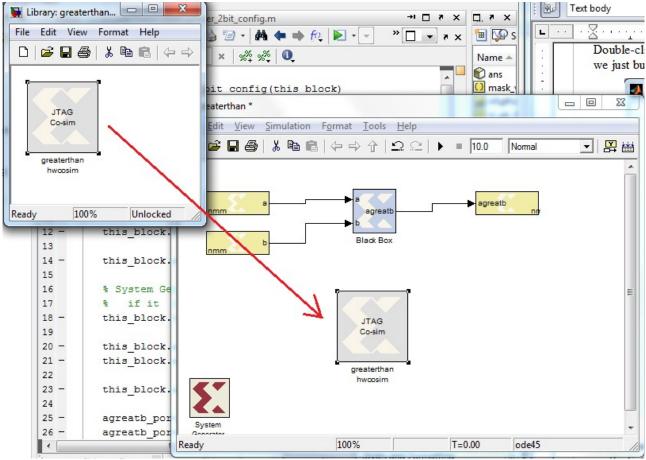

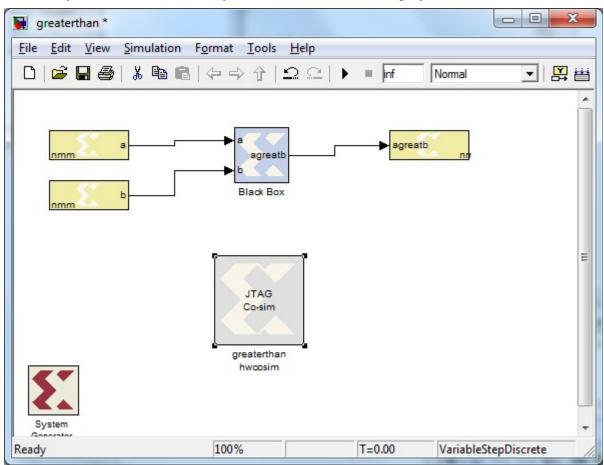

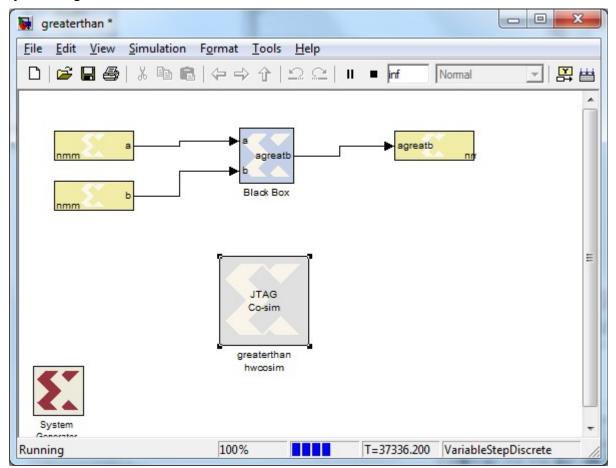

We will use the 2-bit greater-than circuit that was designed in the previous topic 'Programming the FPGA using a VHDL design...' Also the Xilinx blockset in Simulink will be used to define our circuit inputs and outputs. The logic will be fulfilled by using the 'Black Box' block containing our greater-than VHDL code. The bitsream will be created with System Generator and the design will be simulated via hardware co-simulation.

After finishing this tutorial you will be able to create a design using the Xilinx Blockset in Simulink and add a pre-made hdl design using a Black Box, then simulate the design on hardware within Simulink via hardware co-sim.

## Creating the Design

First make sure that Xilinx System Generator is configured to use your version of MATLAB.

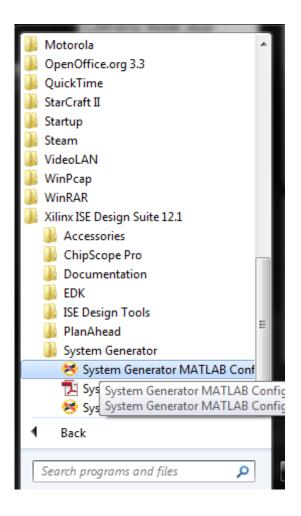

Run the System Generator MATLAB configurator as administrator (right-click  $\rightarrow$  run as administrator):

Select the version of MATLAB you will be using and click ok:

| oose MATLAB for Sy | stem Generator 12.1 |                                |

|--------------------|---------------------|--------------------------------|

| ersion             | Status              | Location                       |

| 7 📣 R2010a         | 🔀 Configured        | C:\Program Files\MATLAB\R2010a |

| × -                | <u> </u>            |                                |

|                    |                     |                                |

|                    |                     |                                |

|                    |                     |                                |

|                    |                     |                                |

|                    |                     |                                |

|                    |                     |                                |

|                    |                     |                                |

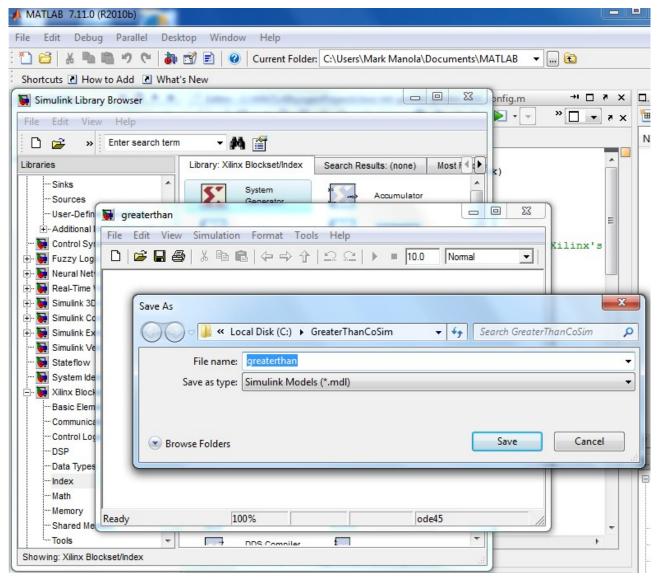

Now open up MATLAB and then Simulink.

| I flore a sector de la sector d |     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 🐌 Fraps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ^   |

| 퉬 Games                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

| 퉬 Guitar Pro 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |

| 퉬 iTunes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |

| 퉬 Logitech                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |

| 퉬 Maintenance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |

| J MATLAB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |

| 퉬 R2010a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |

| 📣 Activate MATLAB R2010a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |

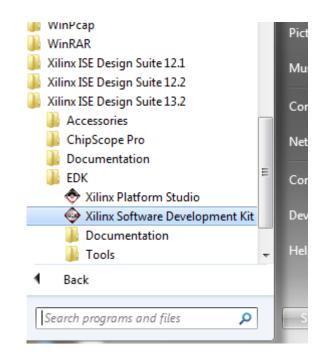

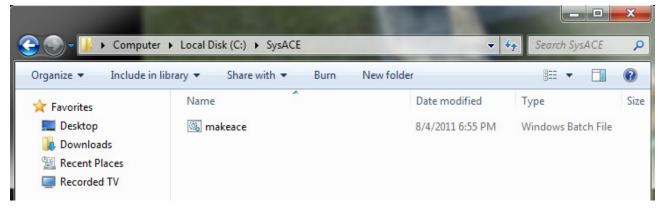

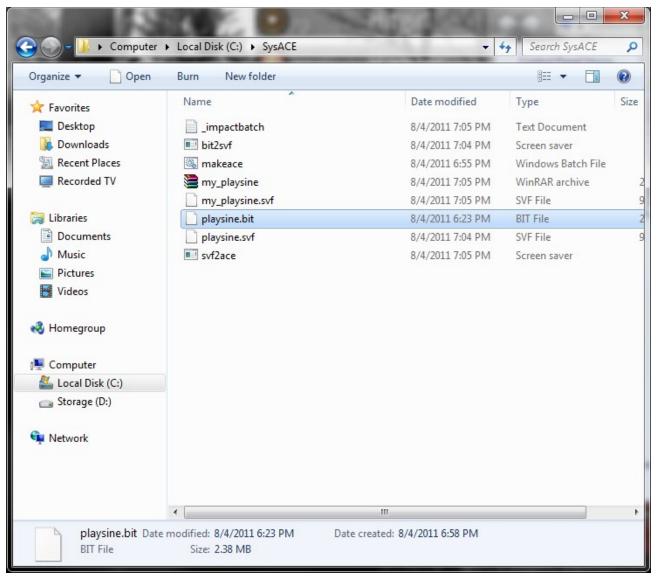

| 📣 Deactivate MATLAB R2010a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |